1D / 2D Discrete Cosine Transform (DCT) implemented with Distributed Arithmetic

Referenced in the following work:

- Llamocca, D., Pattichis, M., Carranza, C., "A framework for self-reconfigurable DCTs based on Multiobjective Optimization of the Power-Performance-Accuracy Space", in Proceedings of the 7th International Workshop on Reconfigurable Communication-centric Systems-on-Chip (RECOSOC'2012), York, United Kingdom, July 2012.

VHDL implementation (stand-alone IPs): 1D/2D DCT VHDL IPs

VHDL implementation (PLB interface): PLB interface VHDL IP

Report on PLB interface: (pdf)

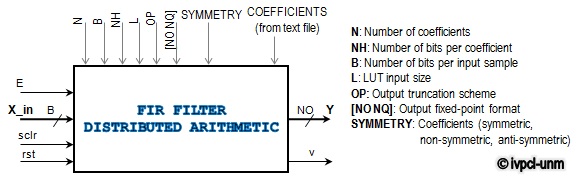

1D FIR FILTER IMPLEMENTATIONS WITH DISTRIBUTED ARITHMETIC

1D Real Input, Real Coefficients FIR Filter implemented with Distributed Arithmetic

The following custom 1D Real Input, Real Coefficients FIR Filter core is a fully pipelined and fully parameterized architecture.

Referenced in the following works:

- Llamocca, D., Pattichis, M., "Dynamic Energy, Performance, and Accuracy Optimization and Management using Automatically Generated Constraints for Separable 2-D Filtering for Digital Video Processing", accepted for publication in ACM Transactions on Reconfigurable Technology and Systems (TRETS).

- Llamocca, D., Carranza, C., Pattichis, M., "Separable FIR Filtering in FPGA and GPU Implementations: Energy, Performance, and Accuracy Considerations", in Proceedings of the 21st International Conference on Field Programmable Logic and Applications (FPL'2011), Chania, Greece, Sept. 2011.

- Llamocca, D., Pattichis, M., and Vera, G.A., "Partial Reconfigurable FIR Filtering system using Distributed Arithmetic", International Journal of Reconfigurable Computing, vol. 2010, Article ID 357978, 14 pages, 2010, doi:10.1155/2010/357978

VHDL implementation (stand-alone IP): Real Filter VHDL IP

VHDL implementation (FSL interface): FSL Interface VHDL IP

VHDL implementation (PLB interface): PLB Interface VHDL IP

LUT file and testbench generation: MATLAB scripts

Report on FIR DA implementation: (pdf)

Report on FSL interface: (pdf)

Report on PLB interface: (pdf)

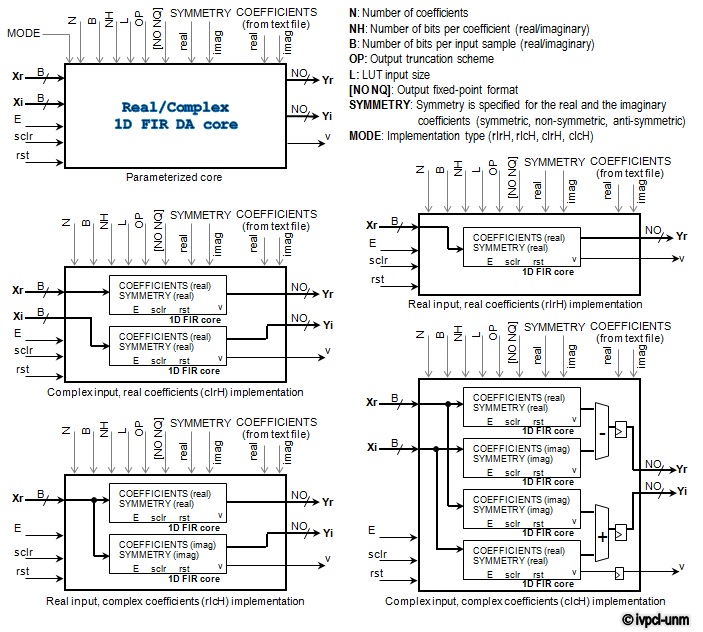

1D Real/Complex Input, Real/Complex Coefficients FIR Filter implemented with Distributed Arithmetic

This generalized implementation is based on the simple 1D Real input, real coefficients FIR Filter implementation.

Complex Input, Complex Coefficients Implementation: Referenced in the following work:

- Llamocca, D., Carranza, C., Pattichis, M., "Dynamic Multiobjective Optimization Management of the Energy-Performance-Accuracy Space for Separable 2-D complex filters", in Proceedings of the 22nd International Conference on Field Programmable Logic and Applications (FPL'2012), Oslo, Norway, Aug. 2012.

Complete Implementation (Real/Complex Input, Real/Complex Coefficients): Referenced in the following work:

- Llamocca, D., Pattichis, M., "A Self-Reconfigurable Platform for the Implementation of 2D Filterbanks with Real and Complex-valued Inputs, Outputs, and Filter Coefficients", VLSI Design, vol. 2014 Article ID 651943, 24 pages, 2014, doi: 10.1155/2014/651943.

Real/Complex Input, Real/Complex Coefficients VHDL implementation (stand-alone IP):

Real/Complex Input, Real/Complex Coefficients Filter VHDL IP

VHDL implementation (PLB interface): PLB Interface VHDL IP

Report on Complex FIR_DA and PLB interface: (pdf)

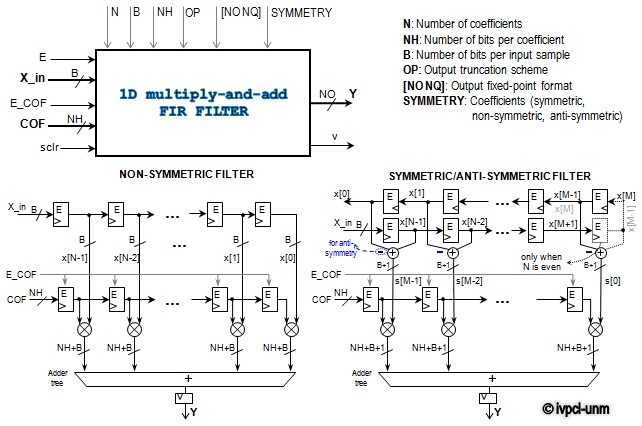

1D MULTIPLY-AND-ADD FIR FILTER IMPLEMENTATIONS

1D Real Input, Real Coefficients multiply-and-add FIR Filter

The following custom 1D Real Input, Real Coefficients FIR Filter core is a fully pipelined and fully parameterized architecture.

Real Input, Real Coefficients Implementation: Referenced in the following work:

- Llamocca, D., Pattichis, M., "Dynamic Energy, Performance, and Accuracy Optimization and Management using Automatically Generated Constraints for Separable 2-D Filtering for Digital Video Processing", accepted for publication in ACM Transactions on Reconfigurable Technology and Systems (TRETS).

VHDL implementation (stand-alone IP): Multiply-and-add FIR Filter VHDL IP

1D Real/Complex Input, Real/Complex Coefficients multiply-and-add FIR Filter

This generalized implementation is based on the simple 1D Real input, real coefficients FIR Filter implementation.

Complete Implementation (Real/Complex Input, Real/Complex Coefficients): Referenced in the following work:

- Llamocca, D., Pattichis, M., "A Self-Reconfigurable Platform for the Implementation of 2D Filterbanks with Real and Complex-valued Inputs, Outputs, and Filter Coefficients", VLSI Design, vol. 2014 Article ID 651943, 24 pages, 2014, doi: 10.1155/2014/651943.

Real/Complex Input, Real/Complex Coefficients VHDL implementation (stand-alone IP): Real/Complex Input, Real/Complex Coefficients Filter VHDL IP

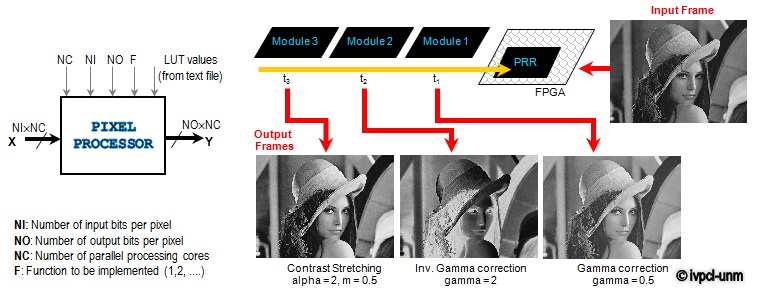

Pixel Processor:

Referenced in the following works:

- Llamocca, D., Pattichis, M., "A Dynamically Reconfigurable Pixel Processor System based on Power/Energy-Performance-Accuracy Optimization", IEEE Transactions on Circuits and Systems for Video Technology, vol. 23, no. 3, pp. 488-502, March 2013.

- Llamocca, D., Pattichis, M., Vera, A., "A dynamically reconfigurable parallel pixel processing system", in Proceedings of the 19th International Conference on Field Programmable Logic and Applications (FPL'2009), Prague, Czech Republic, Sept. 2009.

VHDL implementation (stand-alone IP): Pixel Processor VHDL IP

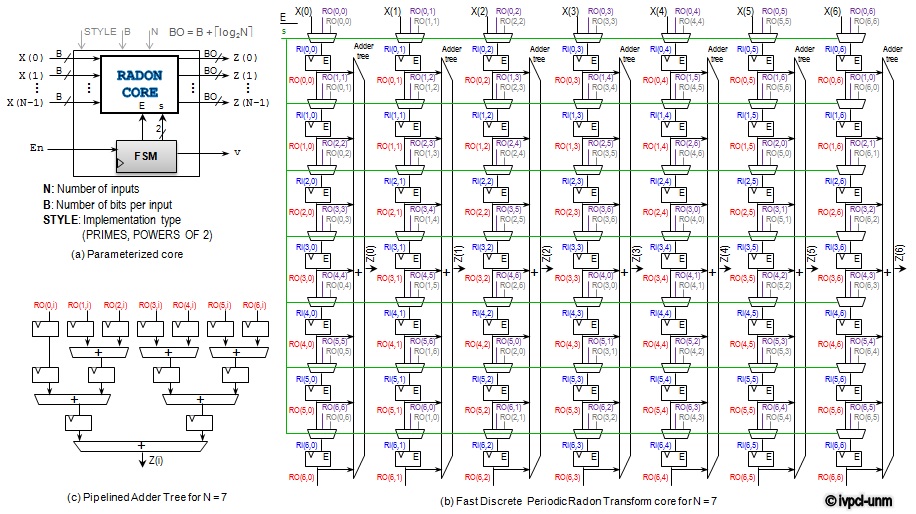

Parameterized Fast Discrete Periodic Radon Transform (for primes and powers of 2):

The following custom Fast Discrete Periodic Transform cores are fully parallel, fully pipelined, and fully parameterized architectures.

Scalable Radon core:

VHDL implementation (stand-alone IP): Scalable Radon Transform VHDL IP

Standard Radon core:

This core was presented in the following work:

- Carranza, C., Llamocca, D., and Pattichis, M., "The Fast Discrete Periodic Transform for Prime Sized Images: Algorithm, Architecture, and VLSI/FPGA Implementation", in Proceedings of the 2014 IEEE Southwest Symposium on Image Analysis and Interpretation (SSIAI'2014), pp. 169-172 , San Diego, California, April 2014.

VHDL implementation (stand-alone IP): Radon Transform VHDL IP